Zhufei Chu [NBU

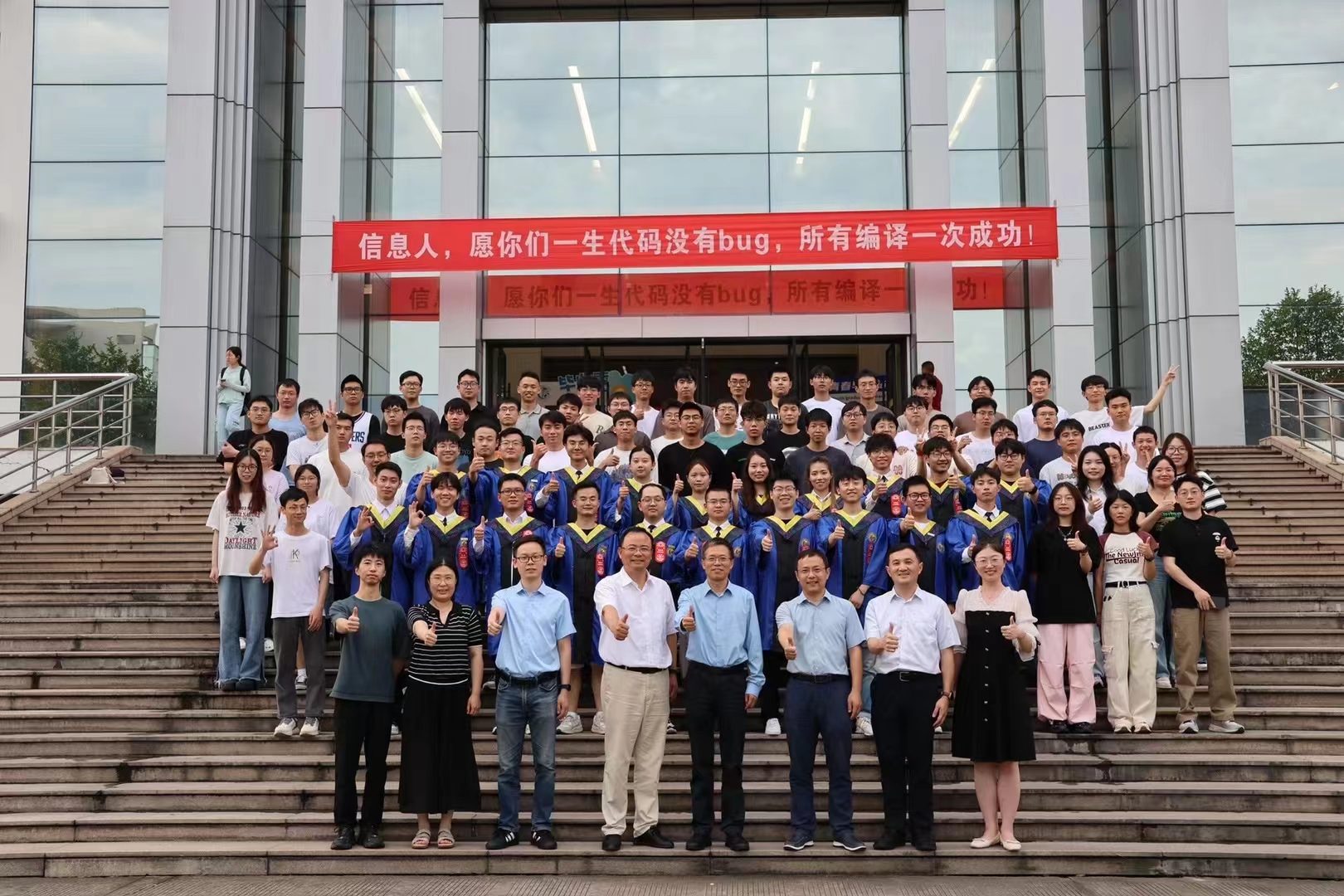

link], born on Oct. 24th, 1986, received his B.S. degree in electronic engineering from Shandong University, Weihai, China, in 2008, and his M.S. and Ph.D. degrees in communication and information systems from Ningbo University, Ningbo, in 2011 and 2014, respectively.

He was a postdoctoral fellow at the Ecole Polytechnique Federale de Lausanne (EPFL), Lausanne, from 2016 to 2017, in the group of Prof. Giovanni De Micheli.

He is currently a full professor at Ningbo University, Ningbo.

His current research interests focus on various aspects of logic synthesis and its applications.

[orcid]

[orcid]